| Poster | Thread |

Gunnar Gunnar

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 3-Oct-2022 8:28:46

| | [ #241 ] |

|

|

|

Cult Member

|

Joined: 25-Sep-2022

Posts: 512

From: Unknown | | |

|

|

Quote:

Vector extensions (register length-agnostic) require much less registers.

|

WRONG!

A CPU needs more registers to be able to do work in parallel fashion.

And to be able to unroll code to avoid sequential stalls.

And your argument "but Intel has only 16 Register" - is absolutely wrong.

Intel has ~ 80 Register internally, to be able to do Out of Order in a sensible way.

Please get a clue about the topics you talk about. |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 3-Oct-2022 8:29:14

| | [ #242 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Gunnar

Quote:

Gunnar wrote:

Quote:

Guess what: another logical fallacy!

Actually logical fallacies are the ONLY thing that you're bringing here.

|

Cesare,

there is nothing wrong by getting information from other sources.

Your problem is the internet is not a 100% reliable source

where every post online is 100% correct - the Internet is full of nonsense.

By quoting from the Internet you can proof the Elvis is still alive,

that the Russians are right now trying to save the Ukraine from Nazis,

that the USA is secretly ruled by reptile aliens, |

Correct. But on internet there are also PAPERs and those are the ones which were reported here.

Quote:

| and that the TINA Amiga project has a 128Bit memory bus. |

Same as before. Replied here: https://amigaworld.net/modules/newbb/viewtopic.php?topic_id=44169&start=200&post_id=855345&order=0&viewmode=flat&pid=0&forum=17#855345

Quote:

| = the Internet is full of nonsense. |

Since we ARE on internet, then this should non-sense as well, right?

Quote:

Without any personal experience yourself your can not judge the quality of what you quote from the Internet.

You ran into this trap of quoting "false fact" without understanding them before. |

Again, another logical fallacy. You're hopeless!

Quote:

Lets us recall your hundreds of posts about the TINA project:

In the TINA project you claimed absolutely false and technical impossible values as hardware facts.

You claimed impossible clockrates, you claimed impossible bus width, and you claimed you have the CPU from NATAMI that you would use. |

Same as before. Replied here: https://amigaworld.net/modules/newbb/viewtopic.php?topic_id=44169&start=200&post_id=855345&order=0&viewmode=flat&pid=0&forum=17#855345

Quote:

Cesare, you repeat this again and again.

Please stop quoting stuff that you not understand. |

I doubt that you could understand each time that you're writing those logical fallacies.

Mother Nature was really bad with you. But, do you know what? It's not my problem, rather... YOUR.  |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 3-Oct-2022 8:35:38

| | [ #243 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| |

| Status: Offline |

|

|

Gunnar Gunnar

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 3-Oct-2022 11:31:10

| | [ #244 ] |

|

|

|

Cult Member

|

Joined: 25-Sep-2022

Posts: 512

From: Unknown | | |

|

| @cdimauro

Dear Cesare Di Mauro,

Quote:

Quote:

there is nothing wrong by getting information from other sources.

Your problem is the internet is not a 100% reliable source

where every post online is 100% correct - the Internet is full of nonsense.

By quoting from the Internet you can proof the Elvis is still alive,

that the Russians are right now trying to save the Ukraine from Nazis,

that the USA is secretly ruled by reptile aliens,

and that the TINA Amiga project has a 128Bit memory bus.

|

Correct. But on internet there are also PAPERs and those are the ones which were reported here.

|

You combine Internet nonsense, Internet Yellowpress, and random papers you find.

Then you mix this all up and on top you misread them.

This is the same like did with the ALTERA documentation at the TINA project.

Everything you posted as hard facts about TINA was wrong.

And on top you made up extra stories.

You even posted here on Amigaworld that you have the NATAMI CPU to include in your TINA project.

|

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 3-Oct-2022 17:30:18

| | [ #245 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Gunnar

Quote:

Gunnar wrote:

@cdimauro

Dear Cesare Di Mauro,

Quote:

Correct. But on internet there are also PAPERs and those are the ones which were reported here.

|

You combine Internet nonsense, Internet Yellowpress, and random papers you find.

Then you mix this all up and on top you misread them. |

At least I can read them: you read nothing and you're blocked on the the Stone Age about parallel computation.

What's even worse, you're unable to understand those papers (as you've shown on the discussion with Samurai Crow).

That's why your AMMX sucks: it's not scalable and it's not future-proof.

Quote:

This is the same like did with the ALTERA documentation at the TINA project.

Everything you posted as hard facts about TINA was wrong. |

"If you repeat a lie often enough, people will believe it, and you will even come to believe it yourself." - Joseph Goebbels

Same as before. Replied here: https://amigaworld.net/modules/newbb/viewtopic.php?topic_id=44169&start=200&post_id=855345&order=0&viewmode=flat&pid=0&forum=17#855345

Quote:

| And on top you made up extra stories. |

Do you talk about the ones that you invent each time and for whom you give absolutely no proof?

Quote:

| You even posted here on Amigaworld that you have the NATAMI CPU to include in your TINA project. |

Yes. To be more exact, it was Jens' N050 soft core.

Matthew sent me the VHDL code on June 2013: N050softcore.7z (7326791 bytes) |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 3-Oct-2022 17:58:57

| | [ #246 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| Updated Benchmarks post with Some benchmarks from Enhancing the RISC-V Instruction Set Architecture. |

|

| Status: Offline |

|

|

Hammer Hammer

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 4-Oct-2022 16:52:21

| | [ #247 ] |

|

|

|

Elite Member

|

Joined: 9-Mar-2003

Posts: 5616

From: Australia | | |

|

| @cdimauro

Quote:

Bobcat had 166Mhz less frequency, but:

- it was out-of-order;

- had more L1 data cache;

- had 512KB L2 cache per core;

- had a better productive process (40nm vs 45nm).

And it sucked compared to Atom...

|

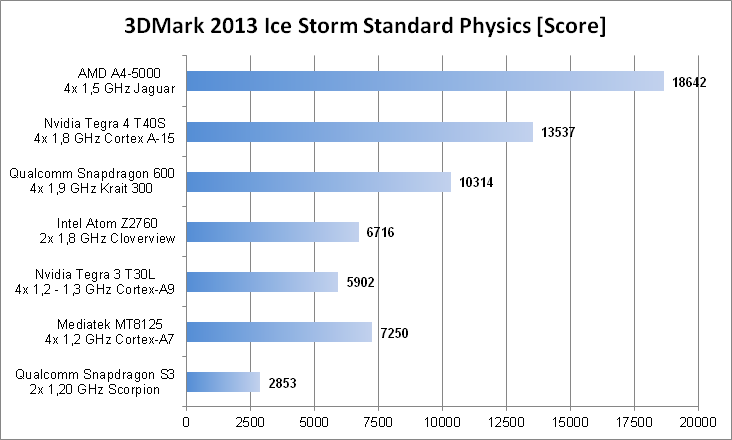

My examples are real desktop apps running on Windows compared to your GCC 4.4/Linux benchmarks.

2014 era ICC beats GCC 4.4.

Anandtech didn't show Jaguar benchmarks

https://www.notebookcheck.net/SoC-Shootout-x86-vs-ARM.99496.0.html

AMD's game console design wins from Microsoft and Sony are real.

ARM Cortex A72 with quad core at 2.3 Ghz (Kirin 950) vs Intel Atom with quad core at 2.3 Ghz (Z3580)

CPU physics score

Intel Atom Z3580 = 20,977

ARM Cortex A72 Kirin 950 = 14,784

AMD Athlon 5350 quad-core Jaguar CPUs = 23,546

AMD's game console design wins from Microsoft and Sony are real.

Amiga 500/1000 is designed to be gaming machines 1st, not Unix workstations!

Last edited by Hammer on 04-Oct-2022 at 05:03 PM.

Last edited by Hammer on 04-Oct-2022 at 05:01 PM.

Last edited by Hammer on 04-Oct-2022 at 04:58 PM.

Last edited by Hammer on 04-Oct-2022 at 04:55 PM.

_________________

Amiga 1200 (rev 1D1, KS 3.2, PiStorm32/RPi CM4/Emu68)

Amiga 500 (rev 6A, ECS, KS 3.2, PiStorm/RPi 4B/Emu68)

Ryzen 9 7900X, DDR5-6000 64 GB RAM, GeForce RTX 4080 16 GB |

|

| Status: Offline |

|

|

Hammer Hammer

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 4-Oct-2022 17:20:49

| | [ #248 ] |

|

|

|

Elite Member

|

Joined: 9-Mar-2003

Posts: 5616

From: Australia | | |

|

| @cdimauro

Quote:

cdimauro wrote:

EDIT. Added "The ARM Scalable Vector Extension" paper on the Vector/SIMD links.

|

AMD Zen 4 has AVX-512 with Intel's extensions beyond AVX-512F.

https://www.phoronix.com/review/amd-zen4-avx512

The AVX-512 extensions supported by Zen 4 as confirmed via the /proc/cpuinfo output on the Ryzen 9 7950X include:

avx512f,

avx512dq,

avx512ifma,

avx512cd,

avx512bw,

avx512vl,

avx512_bf16,

avx512vbmi,

avx512_vbmi2,

avx512_vnni,

avx512_bitalg,

avx512_vpopcntdq.

Zen 4 is available on normal retail channels.

_________________

Amiga 1200 (rev 1D1, KS 3.2, PiStorm32/RPi CM4/Emu68)

Amiga 500 (rev 6A, ECS, KS 3.2, PiStorm/RPi 4B/Emu68)

Ryzen 9 7900X, DDR5-6000 64 GB RAM, GeForce RTX 4080 16 GB |

|

| Status: Offline |

|

|

Karlos Karlos

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 4-Oct-2022 17:30:16

| | [ #249 ] |

|

|

|

Elite Member

|

Joined: 24-Aug-2003

Posts: 4491

From: As-sassin-aaate! As-sassin-aaate! Ooh! We forgot the ammunition! | | |

|

| @Hammer

It'd be nice if vendors stopped adding more and more specialised and wider vector operations and looked into making the scalar code that makes up the majority normal workloads a bit faster. _________________

Doing stupid things for fun... |

|

| Status: Offline |

|

|

Karlos Karlos

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 6-Oct-2022 10:28:39

| | [ #250 ] |

|

|

|

Elite Member

|

Joined: 24-Aug-2003

Posts: 4491

From: As-sassin-aaate! As-sassin-aaate! Ooh! We forgot the ammunition! | | |

|

| @cdimauro

Is there a simulator available (or planned) for NeXT64 ? How do you validate that it works in practise? _________________

Doing stupid things for fun... |

|

| Status: Offline |

|

|

Gunnar Gunnar

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 6-Oct-2022 11:25:14

| | [ #251 ] |

|

|

|

Cult Member

|

Joined: 25-Sep-2022

Posts: 512

From: Unknown | | |

|

| @Hammer

Only 3 pictures of Intel CPU in an Amiga-forum in a single post?

Hammer are not in form today?

Why not more INTEL pics?

|

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 6-Oct-2022 20:25:01

| | [ #252 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Hammer

Quote:

Hammer wrote:

@cdimauro

Quote:

Bobcat had 166Mhz less frequency, but:

- it was out-of-order;

- had more L1 data cache;

- had 512KB L2 cache per core;

- had a better productive process (40nm vs 45nm).

And it sucked compared to Atom...

|

My examples are real desktop apps running on Windows compared to your GCC 4.4/Linux benchmarks. |

There are many also on the benchmark that I've posted.

Quote:

| 2014 era ICC beats GCC 4.4. |

ICC exists for Linux as well. And the same for GCC.

What's the point here?

Quote:

Anandtech didn't show Jaguar benchmarks

[...]

AMD's game console design wins from Microsoft and Sony are real.

[...]

ARM Cortex A72 with quad core at 2.3 Ghz (Kirin 950) vs Intel Atom with quad core at 2.3 Ghz (Z3580)

[...]

CPU physics score

Intel Atom Z3580 = 20,977

ARM Cortex A72 Kirin 950 = 14,784

AMD Athlon 5350 quad-core Jaguar CPUs = 23,546

AMD's game console design wins from Microsoft and Sony are real.

Amiga 500/1000 is designed to be gaming machines 1st, not Unix workstations! |

This is PADDING plus changing the argument: I have NOT talked about AMD's Jaguar.

My statement was only about AMD's Bobcat VS Intel's Atom. And the same is about the proper benchmarks that I've posted.

P.S. Have I said that the Jaguar was off-topic? |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 6-Oct-2022 20:29:25

| | [ #253 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Hammer

Quote:

Hammer wrote:

@cdimauro

Quote:

cdimauro wrote:

EDIT. Added "The ARM Scalable Vector Extension" paper on the Vector/SIMD links.

|

AMD Zen 4 has AVX-512 with Intel's extensions beyond AVX-512F.

https://www.phoronix.com/review/amd-zen4-avx512

The AVX-512 extensions supported by Zen 4 as confirmed via the /proc/cpuinfo output on the Ryzen 9 7950X include:

avx512f,

avx512dq,

avx512ifma,

avx512cd,

avx512bw,

avx512vl,

avx512_bf16,

avx512vbmi,

avx512_vbmi2,

avx512_vnni,

avx512_bitalg,

avx512_vpopcntdq.

Zen 4 is available on normal retail channels.

|

OK, and? What's the point?

@Karlos

Quote:

Karlos wrote:

@Hammer

It'd be nice if vendors stopped adding more and more specialised and wider vector operations and looked into making the scalar code that makes up the majority normal workloads a bit faster. |

Those aren't mutually exclusive.

In fact, CPU vendors are improving the performance of their products on the following areas:

- integer / scalar operations;

- SIMD/vector operations;

- core counts.

Because those affect the various workloads in different ways.

Focusing only on a single area isn't good if we want to tackle all types of algorithms / applications. |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 6-Oct-2022 20:39:42

| | [ #254 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Karlos

Quote:

Karlos wrote:

@cdimauro

Is there a simulator available (or planned) for NeXT64 ? How do you validate that it works in practise? |

Not yet. The plan is to focus on a compiler's backend first (CLang/LLVM) to be created for the ISA, to get some real-world data about code density, number of executed instructions, number of memory accesses, data and bss section sizes.

Plus the related assembler and disassembler.

Once I've something "working" (binaries are generated) I could write an emulator to check if the generated code works properly.

Specifically, it'll be written in x86/x64 assembly, because NeXT64 is a superset of those ISAs, so it's very easy to map one NeXT64 instruction to a bunch of x86/x64 ones. Maybe I'll use C to write the emulator "infrastructure". But those details aren't yet decided (I prefer to use Python, because I can easily build a CI system & related tests). |

|

| Status: Offline |

|

|

Hammer Hammer

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 14-Jun-2023 3:59:14

| | [ #255 ] |

|

|

|

Elite Member

|

Joined: 9-Mar-2003

Posts: 5616

From: Australia | | |

|

| @cdimauro

Quote:

| OK, and? What's the point? |

Product availability is a major factor. _________________

Amiga 1200 (rev 1D1, KS 3.2, PiStorm32/RPi CM4/Emu68)

Amiga 500 (rev 6A, ECS, KS 3.2, PiStorm/RPi 4B/Emu68)

Ryzen 9 7900X, DDR5-6000 64 GB RAM, GeForce RTX 4080 16 GB |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 17-Jun-2023 6:59:06

| | [ #256 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Hammer

Quote:

Hammer wrote:

@cdimauro

Quote:

| OK, and? What's the point? |

Product availability is a major factor. |

Of what (considered the specific context of the discussion)? |

|

| Status: Offline |

|

|

Hammer Hammer

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 12-Feb-2024 5:19:42

| | [ #257 ] |

|

|

|

Elite Member

|

Joined: 9-Mar-2003

Posts: 5616

From: Australia | | |

|

| @Karlos

Quote:

Karlos wrote:

@Hammer

It'd be nice if vendors stopped adding more and more specialised and wider vector operations and looked into making the scalar code that makes up the majority normal workloads a bit faster. |

https://www.phoronix.com/news/AMD-Zen-5-Znver-5-GCC

Over Zen 4, this confirms AMD Zen 5 as adding AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, and PREFETCHI.

Also worth noting from the Znver5 compiler patch is one additional AGU pipe (4 in total) over the current generation and now six ALU pipes up from four ALU pipes with Zen 4.

Zen 5 compared to Zen 4:

There's a 50 percent increase in ALU resources.

There's a 33 percent increase in AGU resources.

AMD improves both scalar ALU/AGU and vector units for Zen 5.

AM5 has a cost advantage since the platform remains the same.

Last edited by Hammer on 12-Feb-2024 at 05:27 AM.

_________________

Amiga 1200 (rev 1D1, KS 3.2, PiStorm32/RPi CM4/Emu68)

Amiga 500 (rev 6A, ECS, KS 3.2, PiStorm/RPi 4B/Emu68)

Ryzen 9 7900X, DDR5-6000 64 GB RAM, GeForce RTX 4080 16 GB |

|

| Status: Offline |

|

|

Hammer Hammer

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 12-Feb-2024 5:23:10

| | [ #258 ] |

|

|

|

Elite Member

|

Joined: 9-Mar-2003

Posts: 5616

From: Australia | | |

|

| @cdimauro

Quote:

| OK, and? What's the point? |

https://www.phoronix.com/news/AMD-Zen-5-Znver-5-GCC

The patch reaffirms Zen 5 (Family 1Ah) CPUs having all the same ISA capabilities just as we enjoy with Zen 4 and Zen 4C... No ISA differences, thankfully, nor between server and desktops/mobile.

Product availability beats theory.

Retail product availability beats elitist server-only SKUs.

Last edited by Hammer on 12-Feb-2024 at 05:23 AM.

_________________

Amiga 1200 (rev 1D1, KS 3.2, PiStorm32/RPi CM4/Emu68)

Amiga 500 (rev 6A, ECS, KS 3.2, PiStorm/RPi 4B/Emu68)

Ryzen 9 7900X, DDR5-6000 64 GB RAM, GeForce RTX 4080 16 GB |

|

| Status: Offline |

|

|

Hammer Hammer

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 12-Feb-2024 5:51:01

| | [ #259 ] |

|

|

|

Elite Member

|

Joined: 9-Mar-2003

Posts: 5616

From: Australia | | |

|

| @cdimauro

Quote:

This is PADDING plus changing the argument: I have NOT talked about AMD's Jaguar.

My statement was only about AMD's Bobcat VS Intel's Atom. And the same is about the proper benchmarks that I've posted.

P.S. Have I said that the Jaguar was off-topic?

|

1. Jaguar (dual instructions, out of order) directly replaced Bobcat (dual instructions, out of order) i.e. Jaguar corrected many of Bobcat's design flaws.

2. Citing "Intel's Atom" is nothing without Atom's specific microarchitecture implementation.

_________________

Amiga 1200 (rev 1D1, KS 3.2, PiStorm32/RPi CM4/Emu68)

Amiga 500 (rev 6A, ECS, KS 3.2, PiStorm/RPi 4B/Emu68)

Ryzen 9 7900X, DDR5-6000 64 GB RAM, GeForce RTX 4080 16 GB |

|

| Status: Offline |

|

|

cdimauro cdimauro

|  |

Re: The (Microprocessors) Code Density Hangout

Posted on 12-Feb-2024 6:06:23

| | [ #260 ] |

|

|

|

Elite Member

|

Joined: 29-Oct-2012

Posts: 3759

From: Germany | | |

|

| @Hammer

Quote:

Hammer wrote:

@cdimauro

Quote:

| OK, and? What's the point? |

https://www.phoronix.com/news/AMD-Zen-5-Znver-5-GCC

The patch reaffirms Zen 5 (Family 1Ah) CPUs having all the same ISA capabilities just as we enjoy with Zen 4 and Zen 4C... No ISA differences, thankfully, nor between server and desktops/mobile.

Product availability beats theory.

Retail product availability beats elitist server-only SKUs.

|

Theory of what? In that part of the discussion I've just added a paper about SIMD / Vector ISAs. And you replied adding padding.

So, I repeat you again: what's the point of all of that regarding THAT, SPECIFIC, part of the discussion?

BTW, it was "just" one year and an half year, but you're still missing the context. Please, read again everything BEFORE replying.

Quote:

Hammer wrote:

@cdimauro

Quote:

This is PADDING plus changing the argument: I have NOT talked about AMD's Jaguar.

My statement was only about AMD's Bobcat VS Intel's Atom. And the same is about the proper benchmarks that I've posted.

P.S. Have I said that the Jaguar was off-topic?

|

1. Jaguar (dual instructions, out of order) directly replaced Bobcat (dual instructions, out of order) i.e. Jaguar corrected many of Bobcat's design flaws. |

And? Who cares? Have your read the discussion and got THAT specific context?

What's (STILL!) NOT clear to you that all reported information were about Bobcat and NOT Jaguar?

Quote:

| 2. Citing "Intel's Atom" is nothing without Atom's specific microarchitecture implementation. |

The details of THAT microarchitecture version were reported on the links that I've provided: it's just(!) enough to READ them.

Why don't you carefully READ the provided documentation BEFORE replying?!? |

|

| Status: Offline |

|

|